Cl wadhwa power system pdf free download. An Electronic Definition Interchange Format (EDIF) parser which allows exports from one EDA schematic capture system (such as OrCad) for import into another (such as KiCad) KiCad library wizard At the moment its simple command line tool to create nice looking schematic libraries in kicad. In this video I’ll be showing you how to import footprints downloaded from SnapEDA (into Cadence Allegro and OrCAD Layout.There are t.

Kicad Vs Orcad

2007-10-24 21:25:41 UTC

Kicad Export Netlist

Announcing edif2kicad, testers requested

https://sourceforge.net/projects/edif2kicad/

For those with schematics they wish to export from OrCad and

import into KiCad.

Date: 2007-10-24 10:55

Summary: edif2kicad-20071023

This release is able to parse OrCad EDIF output, write library files

and a schematic file for import into KiCad EEschema. I rate the

quality at 80% correct, needs more testing, but it beats re-entering

a schematic by hand but user beware!

With a few symbol library edits for pin Up/Down EEschema should be

able to give a pretty good display and produce a netlist. Pin Up/Down

info was not included in my EDIF test files, possibly an bug in

OcCads EDIF out (think I'm using Version 7, if I remember right)

Notes: I put the *.lib, *.sch e2sch output in a separate test

directory. The challenge was to get KiCad to forget about the

installed library path and just look in my test directory. I gave

up and used a text editor to generate some test.pro files. The

*.sch output from e2sch already lists the libraries it found and

generated.

Warning: don't put multiple libs in the same directory. I noticed

'interference* between multiple XTIE connection symbols coming from

different OrCad designs.

TODO:

o maybe automatic reconize sheet size.

(workaround: change in EEschema)

o text scale is still a little funky

o some PinNums are there, some are not

o no testing of hierachical sheets

o mimimal testing of EEschema netlist out

Please read the Kicad FAQ in the group files section before posting your question.

Please post your bug reports here. They will be picked up by the creator of Kicad.

Please visit http://www.kicadlib.org for details of how to contribute your symbols/modules to the kicad library.

For building Kicad from source and other development questions visit the kicad-devel group at http://groups.yahoo.com/group/kicad-devel

«12»https://sourceforge.net/projects/edif2kicad/

For those with schematics they wish to export from OrCad and

import into KiCad.

Date: 2007-10-24 10:55

Summary: edif2kicad-20071023

This release is able to parse OrCad EDIF output, write library files

and a schematic file for import into KiCad EEschema. I rate the

quality at 80% correct, needs more testing, but it beats re-entering

a schematic by hand but user beware!

With a few symbol library edits for pin Up/Down EEschema should be

able to give a pretty good display and produce a netlist. Pin Up/Down

info was not included in my EDIF test files, possibly an bug in

OcCads EDIF out (think I'm using Version 7, if I remember right)

Notes: I put the *.lib, *.sch e2sch output in a separate test

directory. The challenge was to get KiCad to forget about the

installed library path and just look in my test directory. I gave

up and used a text editor to generate some test.pro files. The

*.sch output from e2sch already lists the libraries it found and

generated.

Warning: don't put multiple libs in the same directory. I noticed

'interference* between multiple XTIE connection symbols coming from

different OrCad designs.

TODO:

o maybe automatic reconize sheet size.

(workaround: change in EEschema)

o text scale is still a little funky

o some PinNums are there, some are not

o no testing of hierachical sheets

o mimimal testing of EEschema netlist out

Please read the Kicad FAQ in the group files section before posting your question.

Please post your bug reports here. They will be picked up by the creator of Kicad.

Please visit http://www.kicadlib.org for details of how to contribute your symbols/modules to the kicad library.

For building Kicad from source and other development questions visit the kicad-devel group at http://groups.yahoo.com/group/kicad-devel

Comments

Kicad Netlist Format

- What program do you need to open a .LIB file?You should use a PDF or Open Office file.

- @Publison: This is intended for importation into KICAD as a component file. With it, the P2 outline/pinout becomes just another drag/drop component. I havent tried it since I’m not at my desk, but this could be very handy for KICAD users.

- edited 2020-08-15 - 22:58:21Thanks for explaining that! I have not used KiCad in a while. Trying to stick with DipTrace.

- edited 2020-08-16 - 00:28:38Thanks for explaining that! I have not used KiCad in a while. Trying to stick with DipTrace.

You should try KiCAD. You'll never want to go back once you get used to it! It's really gotten very good since CERN started putting lots of work into it. - Thanks for explaining that! I have not used KiCad in a while. Trying to stick with DipTrace.

You should try KiCAD. You'll never want to go back once you get used to it! It's really gotten very good since CERN started putting lots of work into it.

I have a copy of KiCAD but I use DipTrace because that is what parallax uses and it makes it easier to view their new boards.

I agree KiCAD is a great program! - Parallax is going to change the design files to KiCAD, they just don't know it yet LOL

- While I use Protel99SE, the predecessor to Altium, and I like what I can see with DipTrace, I will probably end up using Kicad myself. Having a multi-part P2 component is a good idea too as the whole component can be a bit unwieldy, although it does help with visualizing signals paths if the component follows the pinout.

- OK, I fixed a few things. Funny how you can repeatedly overlook the same problem, then see it plainly on another day!

- The symbol is interesting. I guess that is useful if planning for deferent power sources for different pin groups..

- edited 2020-08-18 - 22:57:13@R Baggett

Hope you dont't mind me posting to your thread. I thought it may be beneficial to try and keep the KiCad P2 stuff in one thread.

What footprint did you use? (I didn't load the library)

Yesterday was my first attempt with KiCad. I've previously used Protel 95 & 99SE. KiCad has improved dramatically since I took a brief look years ago.

So, here is my first attempt at a P2 symbol and footprint. Beware, it's untested!

Note 1: I based the footprint on that used for the TQFP100 using a 5x5 thermal relief pad, with corrections to use a 9.6x9.6mm pad. The vias were/are currently specified as 0.2mm (~0.008') but I think I will need to change them to 0.3mm (~0.012') for manufacture and I may need to adjust the paste mask accordingly.

Note 2: The footprint uses a slightly modified pad size (1.475x0.3mm) from the recommended OnSemi (in P2 specs) pad size of 1.49x0.28mm. This was the

Note 3: Notice the paste mask are rounded style pads of 0.890668mm. This is what was used in the original TQFP footprint I copied. It is a recommended practice to use a series of paste 'blobs' rather than a single large paste 'blob' but I'm not certain of the recommended sizes without further research.

Note 4: I'm not totally happy about the thremal ground pad 101 reference in the symbol. Maybe I need to see if I can get that to come out from the block on a 45 degree angle at one corner. Just not sure how to do it yet.

pad size used in the KiCad standard library and should work just fine.393 x 347 - 49K781 x 757 - 234Kzip4K728 x 739 - 94K - edited 2020-08-19 - 03:41:08Here is an updated symbol and footprint (still untested).

The symbol now has pin 101 (thermal pad) in the top left corner at 45 degrees to make it a little more obvious that it's not a normal pin.

The footprint now uses the thermal vias as pad 0.55mm and hole 0.3mm.

If anyone uses KiCad, can you tell me how to do a global (whole footprint) edit on a footprint to change the hole sizes and pad sizes?

I had to edit the source file with Notepad++ to do this as I couldn't find any alternative. This was simple enough tho.zip4K - Cluso, Very happy to have it here. I haven't addressed the footprint yet, beyond using that same TQFP100 using a 5x5 thermal relief pad.

Thanks! I plan to import your footprint. As far as blob size, I suspect the vias will steal a lot of the solder, so maybe a little extra is indicated? (My experience in this facet is limited.)

I have found Notepad++ often is faster than finding the 'correct' way to modify some things in Kicad. - The solder paste mask is rounded so with the larger hole at 0.3mm (~0.012”) hopefully the paste will miss the hole. I know as it gets heated some solder will wick down the hole but there should be plenty anyway. There’s a problem if there is too much paste too.

I’ll check later today if there’s a penalty for using 0.2mm (~0.008”) vias - expect pcb mfr to be more expensive. - .I haven't addressed the footprint yet, beyond using that same TQFP100 using a 5x5 thermal relief pad.

Thanks! I plan to import your footprint. As far as blob size, I suspect the vias will steal a lot of the solder, so maybe a little extra is indicated? (My experience in this facet is limited.)

KiCad can import PCAD-ASCII files, which Peter can export from Protel 99, so there is also a P2 footprint available via that pathway.

That works quite well, it's a while since I tried it, but ISTR P2D2 imported fine, with some copper pour ordering/priority edits needed.

KiCad is also finishing a native Altium importer.Parallax is going to change the design files to KiCAD, they just don't know it yet LOL

Someone mentioned Diptrace can import/export already ?

I see they claim this for pcb-layout

'Import / Export

Exchange layouts and libraries with DXF, Eagle, Altium, P-CAD, PADS, KiCAD and OrCAD. Import netlists from Accel, Allegro, Mentor, PADS, P-CAD, Protel, and Tango formats.'

Has anyone tried any of those paths ? - I just searched, but could not find Chip's Hand solder footprint. It seems there was a large hole to allow the pad to be heated with a soldering iron. There are circumstances where I would use this, and I would like to gather it here, or do something similar.

Options B good.. - @Cluso99If anyone uses KiCad, can you tell me how to do a global (whole footprint) edit on a footprint to change the hole sizes and pad sizes?

I don't know the answer to you question but you can set those type's of option's with the design rules.1360 x 768 - 103K - edited 2020-08-20 - 20:55:50Bob,

These holes were already defined in a footprint that I copied, and then copied and pasted more pads for a new part so it wasn’t the default that required changing. There doesn’t seem to be a way to change all in a footprint that I can find.

However, since the footprint file is an easy text format it was simple enough to do a global change in Notepad++. Much better than the hidden format of so many software packages. In the floppy days size mattered but no so any more.

Having fun watching KiCad YouTube tutorials. John’s Basement has a great, if somewhat low level, series. - hi

Thanks for the heads up on John’s Basement YouTube channel- Really helpful.

Dave - edited 2020-08-21 - 07:24:27Here are a couple of bitmap files for the P2 chip.

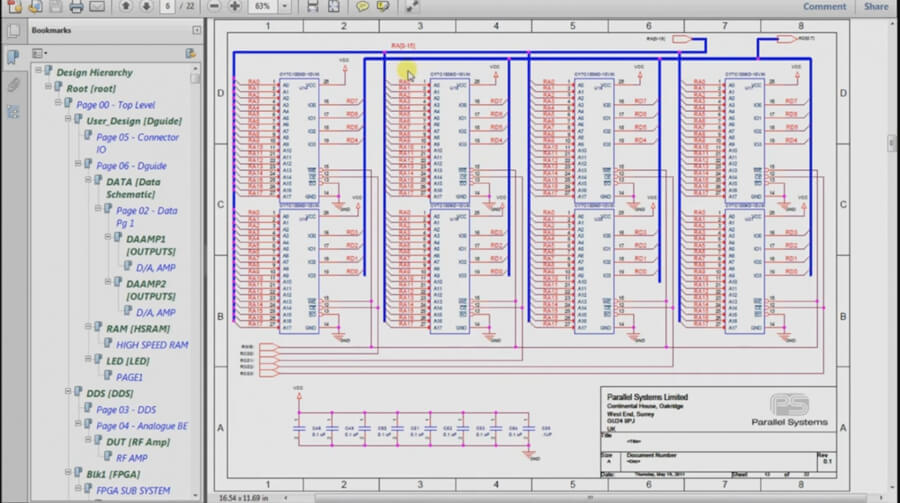

I'm trying to get a bitmap into a footprint for including on a pcb overlay (done). Here is my Clusos icon redrawn from a png file found on the internet600 x 600 - 234K64 x 64 - 6K900 x 640 - 8K - edited 2020-08-22 - 09:01:06In my experience, schematics usually look not very good with generic symbols for chips that essentially have all-equivalent pins, and square symbols that mimic physical pin layout are poor UX to begin with There certainly can be a specialized symbol that maps the pins in their physical locations on the actual chip to aid in hardware debugging, but this is a separate concern from visualizing the flow of signals: the former is a debugging add-on, the latter is the primary function of a schematic as a document for human consumption.

A schematic is there to aid in describing the function of the circuit - it's not meant to be a graphical means for netlist entry, even though most people these days seem to use it this way. That's the downside of the schematics never reaching the customers anymore - eventually what happens is that nobody in the company can quite read it either The P2 eval board 'schematic' suffers from this ailment, and everyone seems to just work in this yucky style.

In my practice, after the layout is complete, generic symbols like FPGAs and P1/P2 are redone in a form that has the pins grouped to best fit with the flow of the schematic, the symbol is broken up into as many constituent parts as needed to best convey the information graphically, and all pins get application-specific names in addition to generic ones, i.e. `CLK_PP/P40` vs just `P40`.

In other words: the generic symbol should at the very least have two parts: power and generic pins, and then the part with the generic pins should have pins on at most two sides of the rectangle, i.e. left and right, since that is easier to deal with in terms of label-slinging while the layout is underway. While the layout is being done, having the flexibility of just moving signal labels around can't be beat. But once the layout is stable, it's time to actually make the schematic human-readable, and not merely machine-readable, and such generic symbols give the human signaling that directly opposes this IMHO noble goal. That's my 2c. - A schematic is there to aid in describing the function of the circuit

Very much agree that the schematic must be human-readable. Mine MUST be, because the technicians generally hand-assemble my boards 1 or 2 off!

I like the multipart because the P2 section(s) required and their power can reside on the hierarchical sheet with the rest of the circuit for that function. Analog, digital, PLC like I/O, whatever is needed. No page flipping - edited 2020-08-23 - 02:35:25While I like the multipart too there is also less need for it if you are using net labels. I like to have the whole P2 symbol match the pinout and then use net labels mostly. No need for old style buses, they just clutter the drawing. So even though my P2D2 has a lot of stuff on it, except for the headers I still fit it on a single sheet with symbols positioned in such a way that you can visualize the flow and layout, and relationship.

However the other thing is that I like to draw symbols for clarity but I also position the value into the component if possible. Those old style zigzag resistors are a waste of space and the same too with caps. This was all fine back in the tube/valve/transistor days when there were very few components in a circuit, but that was another age.1755 x 1080 - 440K - Surely no-one is advocating the style of the P2-EVAL schematic?

IMHO it's a dog's breakfast! You cannot easily work out what is connected to what. - Hehe ... NO! That was net labels used to the extreme, in a lazy way. But there is a balance and the main thing is that a schematic should fulfill its original purpose of providing a representation of the circuit in such a way that it can be read, traced and understood.

- Peter,

Very clear schematic! The techs would burn me at at the stake if I changed the symbols for resistor and caps, but I really like that compactness. May adopt something like that for personal projects!

If I am cramped for space I do move the part IDs inside the square, but If it is too cramped I risk the whole stake thing again.. My average tester is 15 or so sheets 11X17 minimum.

What is the significance of the color?

May I shamelessly rip off your SD power switch? - Hehe ... NO! That was net labels used to the extreme, in a lazy way. But there is a balance and the main thing is that a schematic should fulfill its original purpose of providing a representation of the circuit in such a way that it can be read, traced and understood.

+1

That schematic reminds me of one from the manual of instruments I installed and serviced back in the mid to late 70's. Between the schematic, the netlist, and a clear description of the operation one could troubleshoot and make repairs with no training on the instrument, only basic electronics knowledge. Best manual and schematic I had seen until now. Really like this idea, and will use it on a project I am about to start. - @Cluso99 if you haven't found this yet, here's how you make global pad changes. Hover over the pad you just changed, right click to get the pop menu. At the very bottom is 'Pads'. Pull right and you'll see the 'Push Pad Properties..'.

How did you get the 101 in the corner at a 45 degree angle?

When you create/edit a symbol, you can add a pin and the line to the pin. So just add a pin, place the pin (the little circle) and then redraw the line to it. If you cannot get to work let me know.@Cluso99 if you haven't found this yet, here's how you make global pad changes. Hover over the pad you just changed, right click to get the pop menu. At the very bottom is 'Pads'. Pull right and you'll see the 'Push Pad Properties..'.

How did you get the 101 in the corner at a 45 degree angle?- edited 2020-11-08 - 03:02:17Anyone know how to get the screen info on the surface of the 3d chip?

I want to make this

I have the png file for the top layer but I just cannot get Freecad to merge the 3d TQFP100 with the layer even tho I have it on the surface correctly. ie I cannot combine the surface with the object no matter how I try this - and the freecad forum was no help. Perhaps there's another 3d package? - @Cluso99 Does your manufacturer charge you extra for these small [3mm] vias under the P2?